2진수 연산

ALU(Arithmetic Logic Unit)

-AND/OR

-add / subtract

- Carry / borrow

- Overflow / underflow

Interrupt

-Exception(S/W)

Multiply & Divide

승수는 32비트 승수 레지스터에 있고, 64비트 곱 레지스터는 0으로 초기화되어 있다고 가정

- 왼쪽 그림에 따라 매 단계마다 피승수를 왼쪽으로 한 자리씩 이동, 필요시 중간 결과에 더함

- 이렇게 32단계를 거치면, 32비트 피승수가 왼쪽으로 32번 이동함 -> 64비트 피승수 레지스터가 필요

- 64비트 피승수 레지스터의 오른쪽 절반은 32비트 피승수로, 왼쪽 절반은 0으로 초기화됨

- 64비트 피승수 레지스터는 64비트 곱 레지스터에 축적되는 합과 피승수의 위치를 맞추기 위해 매 단계마다 1 비트 왼쪽으로 자리이동

빠른 곱셈 하드웨어

부동소수점

수수부분과 지수 부분

- 유효숫자에 따른 어림수 개념(.999999999... = 1?)

- IEEE 754 부동소수점 표준

Float(단정밀도) / Double(배정밀도)

- 부호 비트(sign bit) : 0 또는 1로 표현되며, 양수와 음수를 나타냅니다.

- 지수 부분(exponent) : 2진수로 표현된 부동소수점의 지수를 나타냅니다.

- 가수 부분(mantissa) : 2진수로 표현된 부동소수점의 유효 숫자를 나타냅니다.

Biased notation - 음수지수를 계산하기 빠르게 하기 위한 표현방식

Add/Subtract/Multiply/Divide - adder, 부동소수점 전용 H/W사용하는 경우, a = a + (b * c)

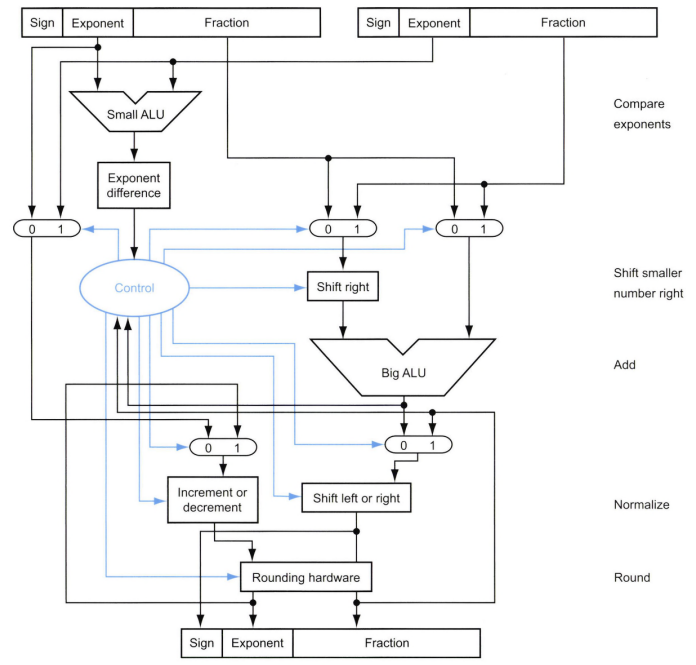

부동소수점 adder

- Small ALU에서 두 수의 크기 비교

- 계산된 차이는 3개의 멀티 플렉서를 제어

- 왼쪽 -> 큰 지수 선택

- 가운데 -> 작은 수의 유효자리

- 오른쪽 -> 큰 수의 유효자리

- 작은 유효자리가 오른쪽으로 자리 이동된 후 큰 ALU에서 큰 수의 유효자리와 더해짐

- 정규화 단계는 합을 왼쪽으로 자리이동시키며 지수를 증가하거나 감소시킴

- 자리맞춤 단계에서 최종 결과 생성

서브워드(데이터 수준) 병렬성

128비트 adder를 사용해서 작은 비트의 연산자를 동시에 연산 가능

행렬곱셈의 성능을 높이는 기술

-8개의 부동소수점 연산을 동시에 처리

FP16/FP32

fp42: IEEE 754 단일 정밀도

fp16: IEEE 754 반 정밀도

- fp16 기준으로 측정할 때, fp32에 비해 두 배 이상 높은 성능을 보임

- fp16은 fp32에 비해 정밀도가 낮기 때문에, 정확한 계산이 필요한 작업에서는 fp32를 사용해야 함

'전공 > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] #6 단일 사이클 구현 1 (0) | 2023.04.23 |

|---|---|

| [컴퓨터구조] #5 프로세서 (0) | 2023.04.15 |

| [컴퓨터구조] #3 명령어 종류, 기능과 형식 (0) | 2023.04.15 |

| [컴퓨터구조] #2 성능평가 (0) | 2023.04.15 |

| [컴퓨터구조] #1 컴퓨터구조 (0) | 2023.04.15 |