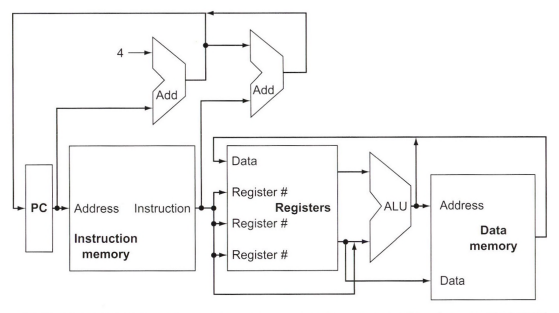

샘플 MIPS 프로세서 구조

메모리 참조 명령어: lw(load doubleword), sw(store doubleword)

산술/논리 명령어: add, sub, AND, OR, slt

조건부 분기 명령어: beq(branch equal), j(jump)

PC(Program Counter)

- 메모리상의 현재 프로그램 실행위치(명령어 위치)

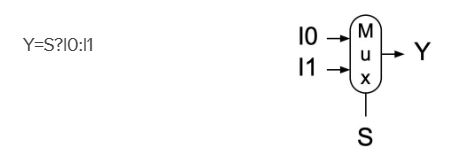

Mux(Multiplex: 다중화기)

- Data selector

- 여러 개개 -> 하나

Demux(De-multiplex:역다중화기)

- 하나 -> 여러 개

명령어 구현

- PC를 프로그램이 저장되어 있는 메모리에 보내서 메모리로부터 명령어를 가져옴

- 읽을 레지스터를 선택하는 명령어 필드를 사용하여 레지스터를 읽음

MIPS 부분집합의 기본적 구현

프로세서 내의 데이터 흐름/ 명령어 실행에 중요한 두 가지 측면이 빠져있음

그림에서는 서로 다른 근원지에서 나온 데이터가 같은 유닛으로 가는 곳이 몇 군데 있음

다수의 근원지 중 하나를 선택하여 그것만을 목적지로 보내는 구성 요소를 추가하여야 함 -> 멀티플렉서(multuplexor) 이용

멀티플렉서(multuplexor): 제어선의 값에 따라 여러 개 입력 중 하나를 선택하는 소자

어떤 유닛들은 명령어 종류에 따라 다르게 제어되어야 하는데 이 부분이 빠져있음

여러 가지 연산 중 하나를 수행 -> 제어선의 명령어 필드 값에 따라 정해지며 제어선이 연산을 통제

이전 그림에서 제어선과 필요한 멀티플렉서 3개를 추가한 그림

- 제어 유닛(Control unit) -> 명령어를 입력으로 받아 기능 유닛들과 두 멀티플렉서의 제어선 값 결정

- 3번째 멀티플렉서는 PC + 4와 분기 목적지 주소 중 어느 것을 PC에 써야 할지 ALU의 Zero출력으로 제어

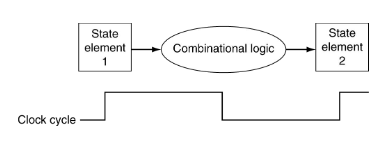

데이터패스(Datapath) 요소

조합소자와 상태소자로 이루어짐

- 조합소자: 출력이 입력에 의해서만 영향받음

- AND, OR, NOT, NOR,...

-상태소자: 값(0/1)을 기억하는 상태를 가지는 소자

- 명령어/데이터 메모리, 레지스터,...

- D 플립플롭(Flip-flop)

- 최소 2개의 입력과 1개의 출력

- 논리회로: 조합소자만으로 구성된 회로

- 순차회로: 상태를 포함하는 combination circuit

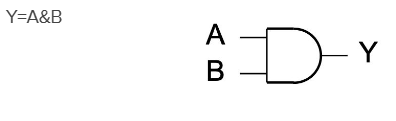

조합소자

AND

Adder

Multiplexer

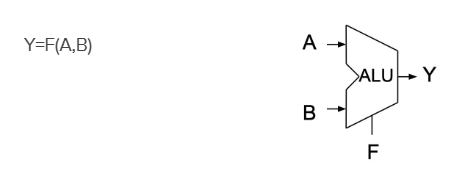

ALU(Arithmetic Logic Unit)

동기식/비동기식

H/W에서의 의미 - 클럭을 공유하는가? 아닌가?

S/W에서의 의미 - 함수를 호출하고 리턴할 때까지 기다려야 하는가? 아닌가?

동기식 시스템

- 같은 클럭소스를 공유하는 시스템

-대표적으로 컴퓨터

- 하나의 메인보드의 클럭이 CPU, GPU, 메모리, SSD, HDD로 들어감

- 서로 다른 클럭속도는 분주(divide)되어 들어감

- 군대의 행진과 같은 형태로 동작

- 주로 짧은 거리에서 동작 - 고신뢰도(보내면 받았다고 전제)

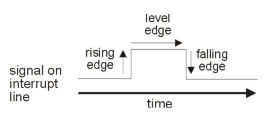

비동기식 시스템

- 같은 클럭을 사용하지 않는 형태의 시스템

- 대표적으로 인터넷(TCP/IP)

- 여러 시스템이 연결된 네트워크

- 주로 먼 거리라 신뢰도가 낮음

- 받았는지 안 받았는지(ACK/NACK)를 확인 필요

클러킹 방법론

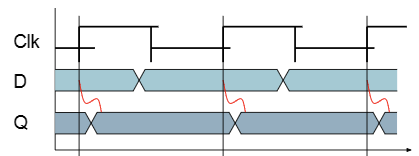

에지 구동 클러킹(edge-tiggered clocking)

- Rising edge / falling edge 중 하나에서만 동작하도록 설계

- 클럭(활성화 클럭 에지) 신호와 쓰기 신호가 인가되어야 상태값 변경 가능

- 클럭이 한 사이클 이내에 모든 회로의 전파가 완료될 정도로 충분히 길어야 함

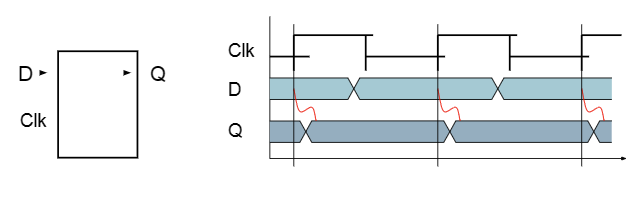

순차회로

Register: stores data in a circuit

- 클럭 신호를 사용하여 저장된 값을 업데이트할 시기를 결정

- Edge-triggered: Clk가 0에서 1로 변경될 때 업데이트

Register with control

- 쓰기 제어 입력이 1인 경우 클럭 에지에서만 업데이트됨

- 나중에 저장된 값이 필요할 때 사용됨

'전공 > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] #7 단일 사이클 구현 2 (0) | 2023.04.23 |

|---|---|

| [컴퓨터구조] #6 단일 사이클 구현 1 (0) | 2023.04.23 |

| [컴퓨터구조] #4 컴퓨터 연산 (0) | 2023.04.15 |

| [컴퓨터구조] #3 명령어 종류, 기능과 형식 (0) | 2023.04.15 |

| [컴퓨터구조] #2 성능평가 (0) | 2023.04.15 |